Samsung présente son procédé de gravure de puces en 3nm

Samsung a annoncé avoir développé un procédé de gravure de puces en 3nm. Il en est à sa première version préliminaire et on ignore quand il sera utilisé dans la production de masse.

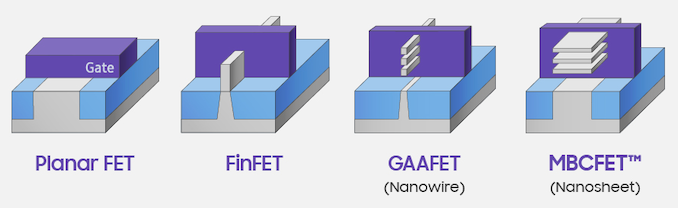

La plus grande nouveauté est la modification profonde des portes de transistors qui passent de la technologie FinFET à une autre appelée GAAFET.

Selon Samsung, ce nouveau design permet de gagner en finesse mais ne compromet pas les techniques actuellement utilisées pour créer le design d'une puce à graver.

Il sera possible de faire varier au sein d'une même puce la largeur des portes. Ainsi, une partie pourra être destinée à la performance et une autre à une consommation moindre.

La limite de finesse des puces recule donc, visiblement sans problème majeur si ce n'est des coûts en R&D toujours plus élevés.